研究背景

在半导体技术持续追求微缩化的进程中,硅基晶体管的尺寸已逼近物理极限,短沟道效应、漏电流等问题日益凸显。为延续摩尔定律,产业界先后发展了如FinFET等三维晶体管架构、高K金属栅极技术以及三维集成等先进方案。然而,这些方法多侧重于器件结构和集成方式的优化,虽在一定程度上维持了性能提升,但也带来了设计复杂性剧增和制造成本高昂的问题,且未能从根本上解决载流子在纳米尺度沟道中传输时发生的界面散射等核心物理瓶颈。因此,研究焦点正逐渐从纯工程优化转向更基础的材料创新。探索具有独特电学特性(如超高迁移率、天然超薄体、缺陷容忍度高)的新型半导体材料(例如二维材料、莫特绝缘体、非晶氧化物半导体),并研究它们与高K介质、铁电材料等新型栅介质的协同集成,被视为突破当前技术困境、实现下一代晶体管性能飞跃的关键路径。这标志着半导体技术的发展进入了一个依赖多种新材料“融合创新”的新范式。

Beyond the Silicon Plateau: A Convergence of Novel Materials for Transistor Evolution

Jung Hun Lee, Jae Young Kim, Hyeon-Ji Lee, Sung-Jin Choi, Yoon Jung Lee* & Ho Won Jang*

Nano-Micro Letters (2026)18: 69

https://doi.org/10.1007/s40820-025-01898-8

本文亮点

1. 材料体系多样:聚焦二维材料、钙钛矿等前沿体系,揭示其超薄、缺陷耐受等独特物性优势。

2. 解决方案协同:通过材料-介质-互连的协同整合,系统性应对芯片微缩的核心挑战。

3. 面向未来应用:前瞻性讨论可靠性问题及其在AI、存算一体等下一代架构的应用潜力。

内容简介

在晶体管尺寸持续微缩逼近物理极限的背景下,业界在三维集成、架构优化(如FinFET)等方面已取得显著进展。然而,这些“高端”技术方案日趋复杂且成本高昂。韩国首尔国立大学Yoon Jung Lee&Ho Won Jang团队在本文中指出了一个更为根本的发展方向,将研究重点回归到晶体管的核心,沟道本身。作者指出与其依赖复杂的结构设计,不如从材料本源出发,通过探索和开发能替代硅的新型半导体材料,从根本上解决沟道中载流子散射的问题,实现高效传输。这代表了一种寻求底层突破的创新思路,旨在为半导体技术的持续发展提供简单而强大的核心驱动力。

图文导读

I 引言

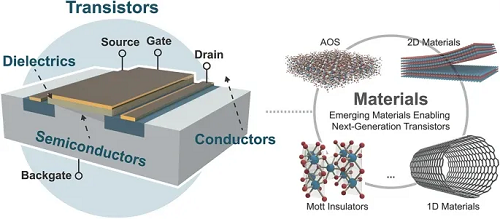

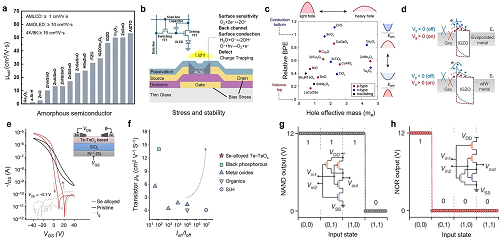

本综述系统探讨了用于未来晶体管的多种新型材料(图1b-d)。核心在于展示新型半导体(如二维材料、钙钛矿,具备超薄、缺陷耐受等独特优势)与先进栅介质(如高K材料、铁电体)的协同集成,以解决界面缺陷、EOT退化等关键问题;同时引入拓扑半金属作为新型互连材料以减少散射。文章超越单一器件性能,进一步审视了热稳定性、漏电流等可靠性挑战,并展望了在3D集成、低功耗AI硬件等领域的应用前景。最终强调,需要通过材料、结构与系统的联合优化,才能推动晶体管技术的根本性进步。

图1. 晶体管中应用的材料特性及其对应功能。a 材料按晶体管组件分类,分别对应 b 半导体、c 介电体与 d 导体。基于这些材料特性构建的晶体管展现出卓越性能与多功能性。

II 晶体管技术的演变

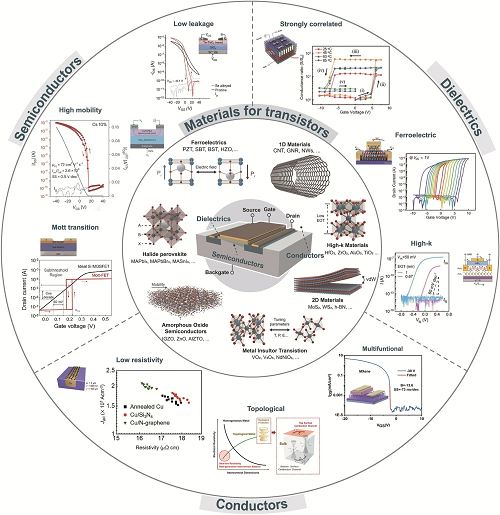

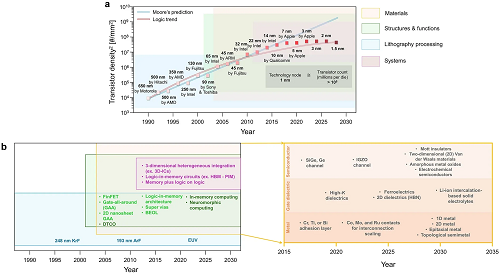

作者梳理了晶体管技术从发明、CMOS工艺成熟到遵循摩尔定律持续微缩的发展历程(图2)。指出在尺寸进入纳米尺度后,短沟道效应、量子隧穿及经济成本成为严峻挑战。行业通过FinFET、GAA等三维结构以及新材料进行应对,但持续缩放已逼近物理极限。未来发展方向将依赖于新型沟道材料(如二维材料)、先进栅介质与3D集成技术的协同创新,从追求密度缩放转向系统级能效优化。

图2.晶体管结构与材料的发展趋势及未来展望。自1947年起步以来,晶体管技术遵循摩尔定律持续微缩;至2000年代后转向三维架构,而进一步微缩面临的挑战催生了材料、工作原理、器件结构和系统整合等多维创新,以突破传统缩放极限、继续推进节点尺寸缩小。

III 晶体管技术的演变

3.1 低功耗开关的重要性

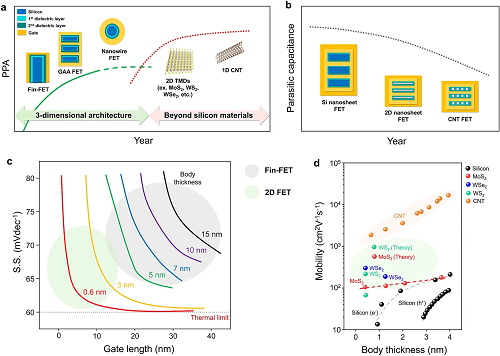

工作电压从5V降至亚1V水平是降低功耗(与Vdd的平方成正比)的主要驱动力。未来进一步将Vdd降至0.7V以下,对晶体管本身的电气特性提出了更高要求:必须具备接近热力学极限(60 mV/dec)的低亚阈值摆幅(S.S.)和较小的阈值电压(Vth)。

为实现低S.S.,关键在于优化器件界面质量,减少寄生电荷和界面缺陷引起的电荷散射。这需要减小耗尽层电容并提升栅介质电容的质量。而实现低Vth,则需要综合运用高K栅介质(以增大单位面积栅电容Cox)、低衬底掺杂浓度(Na)以及合适的栅极金属(以调节平带电压VFB)等策略。台积电的实例证明了高K介质与轻掺杂衬底结合的可行性。

总之,低功耗开关的实现路径是:通过持续降低Vdd来大幅降低功耗,而Vdd的降低又依赖于在材料、界面和器件物理层面协同优化,以最终获得具有理想S.S.和Vth特性的晶体管。这标志着工作电压的缩放已成为推动晶体管技术向前发展的核心挑战之一。

3.2 晶体管微缩的趋势

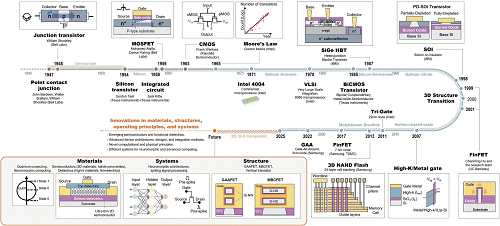

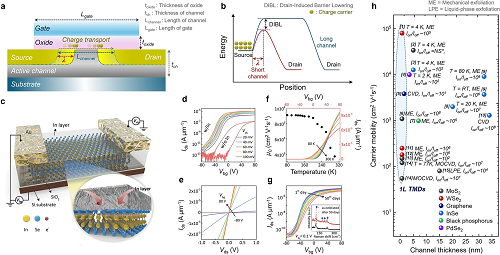

为克服硅基晶体管在3纳米以下技术节点面临的短沟道效应、界面缺陷和寄生电容等物理极限,半导体技术正从3D结构创新转向低维材料探索。尽管FinFET、GAA等三维架构实现了3纳米工艺的商业化,却仍受限于机械稳定性、沟道应力及寄生电容等挑战。二维过渡金属硫族化合物(图3a)和一维碳纳米管等新材料通过范德华界面(图3b)有效抑制界面散射,将载流子迁移率提升至硅的10-100倍(图3d),使亚阈值摆幅逼近60mV/dec理论极限(图3c)。这类材料兼具原子级厚度和热稳定性,可支撑垂直CFET架构的3D集成,但其在显示应用中的大面积均匀制备(表1)和电极接触优化仍是产业化关键瓶颈。未来发展需通过材料-界面-架构的协同创新,在平衡性能与功耗的同时突破摩尔定律的物理边界。

图3. 基于超硅材料的晶体管微缩趋势。a 半导体器件架构演进:从三维集成走向超硅材料创新;b 先进晶体管微缩技术示意图,显示随时间推移寄生电容的降低;c 两种典型FET(FinFET与二维FET)的亚阈值摆幅随栅极长度变化趋势;d 未来晶体管替代材料(如碳纳米管、二维过渡金属硫化物)的性能探索,展示其理论与实验进展。

3.2 微缩极限及其新材料解决方案

尽管摩尔定律长期指导着晶体管的微缩,但近几十年来,其预测与逻辑器件缩放的实际趋势之间日益扩大的差距凸显了其局限性(图4a)。自2010年以来,出现了一个关键转变,区分了实际晶体管尺寸和虚拟缩放预测,这推动了一场范式变革,转向通过材料、器件功能、制造工艺和系统演进这四个关键领域的进步来解决缩放难题(图4b)。由于EUV光刻技术存在多重图形化工艺效率低下及环境影响的挑战,仅依赖超越EUV的下一代图形化技术并非持续微缩的最有效策略。因此,探索利用上述多领域进步的多元化解决方案,已成为推动晶体管技术未来发展的更有效路径。

图4. 近期场效应晶体管的缩放限制。a 过去35年晶体管密度趋势及未来5年预测,凸显摩尔定律预测与实际逻辑缩放趋势间的差异;各趋势点标注对应沟道长度与制造厂商。2010年左右出现了按摩尔预测划分实际与虚拟晶体管尺寸的缩放标准。b 近40年来晶体管材料、器件结构与功能、光刻工艺及系统演进的历程;黄色、绿色、蓝色和红色区域分别代表半导体材料、结构与功能、光刻及系统发展的趋势。在影响缩放性的多项因素中,特别总结了2015至2035年间金属接触、栅介质和半导体层等关键材料的详细发展趋势。

IV 下一代半导体

4.1 二维vdW半导体

二维范德华半导体的合成对其晶体管性能优化至关重要,其方法可分为自上而下和自下而上两类。自下而上法如化学气相沉积(CVD)、金属有机CVD(MOCVD)及分子束外延(MBE)等,能精确控制原子结构,制备出结晶质量高、均匀性好的单层或少层二维薄膜(可实现2-4英寸晶圆级生长),但其大面积均匀性和规模化仍面临前驱体流量、热梯度等因素的挑战。范德华外延(vdWE)利用弱范德华力可在晶格失配衬底上生长应变较小的异质结构。自上而下法如化学气相传输(CVT)和助熔剂法主要用于合成高质量块体晶体,为其后通过机械剥离(ME)获得高质量薄片或通过液相剥离(LPE)制备可溶液加工的大面积薄膜(如旋涂、印刷)提供原料,后者在规模化应用和柔性电子中更具优势。

二维vdW半导体因其原子级厚度、无悬挂键等本征特性,在下一代晶体管技术中展现出变革潜力。与传统硅基FET随着沟道长度缩减出现严重的短沟道效应(SCEs)不同(图5a),二维材料的超薄体结构极大地增强了栅极静电控制,能有效抑制漏致势垒降低(DIBL)和关态漏电流,保持良好的开关特性(图5b)。例如,基于二维横向异质结构的晶体管可实现亚1纳米沟道长度。在材料方面,硒化铟(InSe)具有高迁移率,但存在环境不稳定性;采用铟(In)封装层进行表面电荷转移掺杂(SCTD)可显著提升其电学性能(迁移率在80 K时高达~9100 cm2 V⁻1 s⁻1)和长期稳定性(图5c-g)。黑磷(BP)则是优秀的天然p型材料,具有高空穴迁移率和层数依赖的带隙可调性,但需通过芳基重氮盐共价功能化等方法解决其环境不稳定性问题。通过溴(Br₂)掺杂二维WSe₂可将其空穴迁移率从~0.004 cm2 V⁻1 s⁻1提升至27 cm2 V⁻1 s⁻1。此外,采用slot-die印刷技术结合特定介电层(如SEA)已成功制备出均匀性良好的晶圆级二硫化钼(MoS₂)晶体管阵列(迁移率达80.0 cm2 V⁻1 s⁻1),并实现了逻辑电路集成。化学掺杂(如TFSI处理n型MoS₂, Br₂掺杂p型WSe₂)能有效钝化缺陷、降低接触电阻,从而显著提升器件性能。图5h展示了不同合成技术(ME, LPE, CVD, MOCVD)所得的多种二维半导体材料的载流子迁移率与沟道厚度关系,其中机械剥离的少层石墨烯和InSe在低温下迁移率超过10⁴ cm2 V⁻1 s⁻1。总之,二维半导体在延续摩尔定律 beyond 硅极限方面潜力巨大,但其大规模、高均匀性合成与集成仍是实现其产业化应用的关键。

图5. 二维范德华半导体。a 极端尺度下FET的结构示意图,展示载流子输运的关键参数;b 晶体管长沟道与短沟道构型的能带图,突出漏致势垒降低(DIBL)和特征屏蔽长度(λ);c 铟封装背栅InSe FET器件结构,铟层用于表面保护与掺杂,插图为表面电荷转移掺杂(SCTD)工艺细节;d 层状InSe FET(32 nm铟封装)在不同源漏电压下的转移特性,并与未封装器件对比;e 不同背栅电压下铟封装InSe FET的输出特性;f 器件迁移率随温度变化的转移特性曲线;g 铟封装InSe FET在50天内的稳定性评估,包括转移特性、拉曼光谱、迁移率和滞后回线窗口的演变;h 基于机械剥离、液相剥离、化学气相沉积和金属有机化学气相沉积方法的二维晶体管迁移率随沟道厚度变化关系(NS*表示未注明)。

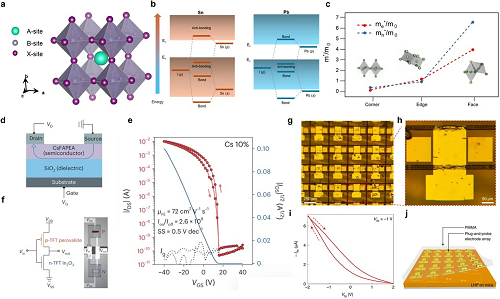

4.2 卤素钙钛矿

卤化物钙钛矿半导体在光电子应用中的进展使其晶体管应用重新受到关注。这类具有ABX₃晶体结构的材料(图6a),因其低温可加工性、缺陷耐受性、双极传输特性以及独特的离子-电子混合传导能力,为替代硅在先进晶体管技术中提供了新平台,尤其适用于低功耗、高密度及具有神经形态功能的晶体管。钙钛矿薄膜主要可通过一步或两步沉积法制备,其电荷传输特性深受B位阳离子(铅基材料通常显示双极传输,而锡基材料倾向于p型传导,图6b)和八面体连接方式(角共享结构有利于电荷传输,图6c)的影响。

尽管面临离子迁移导致的稳定性挑战,但通过添加剂工程、界面工程(如采用金属氧化物注入层或高K介质)等手段可有效抑制缺陷、减小滞后效应并提升性能。研究表明,通过A位工程优化(如调控Cs摩尔比)已成功制备出空穴迁移率高达70 cm2 V⁻1 s⁻1、开关比达10⁸的高性能晶体管(图6d,e),并实现了NAND和NOR逻辑门集成(图6f)。此外,钙钛矿与二维材料(如MoS₂)形成范德华异质结,或通过“即插即用”式范德华集成方法(图6g-j),为构建CMOS兼容、低工作电压的神经形态计算架构和智能视觉系统开辟了道路。尽管长期稳定性和与CMOS工艺的全兼容性仍是挑战,但钙钛矿材料在柔性电子、低功耗计算和硬件人工智能等领域已展现出巨大应用潜力。

图6. 卤化物钙钛矿晶体管。a 卤化物钙钛矿的晶体结构;b 锡基与铅基钙钛矿的能带位置;c 载流子有效质量随八面体连接度增加的变化关系;d 锡基钙钛矿晶体管的结构示意图;e CsFAPEA基晶体管的转移特性曲线;f 反相器的结构示意图与光学图像;g 顶栅钙钛矿晶体管阵列的光学显微图像及h 局部放大视图;i 钙钛矿晶体管的转移特性曲线;j 云母基底上即插即测电极阵列的结构示意图。

4.3 莫特绝缘体

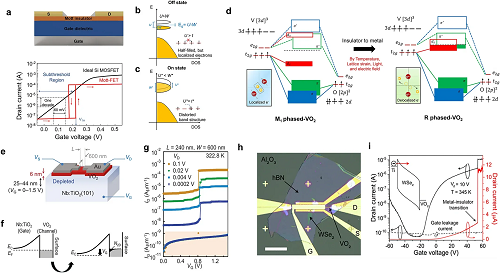

为实现晶体管的超快开关和低功耗运行,莫特绝缘体已成为备受关注的候选半导体材料。尽管名为“绝缘体”,但这些材料在外部刺激(如栅压、光、温度或压力)诱导的电子关联效应下,会表现出独特的电学特性。这种关联驱动现象导致莫特绝缘体发生金属-绝缘体转变,产生极高的电阻率变化和电荷密度显著调制。与硅基晶体管在5纳米以下受短沟道效应和亚阈值摆幅热力学极限限制不同,莫特系统可提供陡峭的开关特性(亚10 mV/dec),即使在原子尺度也能保持强大的静电控制能力。其高本征载流子密度和可忽略的托马斯-费米屏蔽效应,使得在纳米厚度下实现强栅极耦合而不同时牺牲开关比或迁移率成为可能。这些特性共同使莫特绝缘体成为超越CMOS逻辑的强有力候选者,适用于超低功耗运行、极致尺寸缩放和神经形态计算等领域。在众多莫特绝缘体中,VO₂因其能在温度超过68°C或强电场诱导的高表面电荷密度下,发生从绝缘性单斜相到金属性金红石相的MIT而成为研究代表(图7d)。

VO₂基莫特晶体管的独特优势在于其皮秒级的超快开关速度和低于100 fJ的极低写操作能量。其开关行为与传统FET截然不同,可实现突破热离子发射极限的陡峭亚阈值摆幅,从而实现急剧的开关切换(图7a)。这种快速开关归因于沟道中电子的突然离域化,其开关机制可通过态密度图来理解(图7b, c):莫特FET通过栅压诱导的能带结构改变(即电子态变化)来促进电子离域,而非传统FET依赖外部栅场的热激发载流子形成沟道。

基于VO₂的独特现象,研究人员开发了多种创新型晶体管结构。例如,Yajima等人报道了一种非常规构型,利用掺铌TiO₂与VO₂之间的耗尽区作为虚拟栅介质(图7e)。该耗尽层在施加正栅压时扩展,诱导VO₂沟道发生MIT,实现了在极低Vds(0.004 V)下的低功耗等温开关,开关比达103(图7f, g)。另一项研究将VO₂纳米线作为二维WSe2晶体管的漏极(图7h),利用栅致自加热诱导VO₂的MIT行为,实现了载流子的双极性调控和电流的急剧放大,获得了60 mV/dec的亚阈值摆幅(图7i)。这些研究共同表明,无论VO₂作为半导体沟道还是作为漏电极使用,其栅压可调的MIT行为都为实现超快、低功耗的晶体管应用开辟了广阔前景。

图7. 莫特晶体管。a 典型底栅顶接触结构莫特晶体管示意图,展示其陡峭开关特性与低亚阈值摆幅;b、c 分别呈现莫特绝缘体在关态和开态的电子结构;d VO₂在温度、晶格应变、光、电场等调控下从M1绝缘相向R金属相转变的能带结构变化;e 采用Nb-TiO₂栅电极的三端VO₂晶体管;f 图7e器件在栅压作用下的VO₂/Nb-TiO₂接触能带图;g 322.8 K温度下不同漏电压(0.0002~0.1 V)的转移特性曲线;h 以VO₂为漏电极、hBN为栅介质的多层WSe₂晶体管;i 图7h器件在345 K下的转移曲线及栅极漏电流。

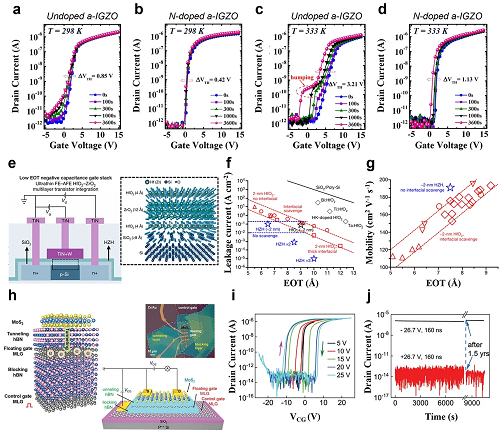

4.4 非晶氧化物

非晶氧化物半导体材料在晶体管沟道应用中相较于传统硅展现出独特优势,尤其适用于器件微缩和异质集成时代。AOS材料具有宽禁带带来的低漏电流、非晶态下高载流子迁移率、以及与低温大面积制备技术优异的兼容性。其无晶界结构确保了电学均匀性,介电界面提供了可靠的开关特性。自2004年首次报道非晶IGZO柔性TFT以来,AOS材料作为氢化非晶硅的替代品被广泛研究用于显示背板(图8a)。高性能AOS TFT需要高场效应迁移率、接近零的阈值电压和低亚阈值摆幅。a-IGZO的高迁移率使其成为显示背板的关键候选者,4K显示通常需要至少16 cm2 V⁻1 s⁻1的迁移率。

除了高迁移率,AOS支持低温大面积加工,非常适用于柔性显示和可穿戴电子等下一代设备技术。然而,用于有源矩阵OLED和LCD的AOS TFT可能因栅偏压应力、光照和环境因素出现不稳定性(图8b)。影响其长期性能的关键因素包括:偏压应力(正/负偏压应力导致Vth漂移)、光照不稳定性(紫外光激活氧空位和界面陷阱)、环境效应(与O₂/H₂O相互作用)、界面缺陷与电荷陷阱、以及柔性应用中的机械应力。研究通过后退火、杂质掺杂和表面钝化来抑制氧空位以增强稳定性。

近期研究已将AOS的应用从显示领域扩展到CMOS逻辑器件,需要同时集成p型和n型AOS以实现低功耗高性能晶体管。当前主要挑战在于开发高空穴迁移率的p型AOS以平衡电路性能(图8c)。p型AOS迁移率低的原因包括高空穴有效质量、空穴局域化以及氧空位的n型掺杂效应。解决策略包括探索新型p型氧化物(如SnO)、异质结结构、过渡金属掺杂和层状结构。

接触电阻是AOS晶体管的另一关键挑战。采用范德华金属接触(图8d)可减轻费米能级钉扎,改善电荷传输并降低接触电阻。合金掺杂(图8e)、优化沟道厚度和低温退火也被证明有效。图8f-h比较了不同半导体系统的性能并展示了AOS基逻辑门(如NAND、NOR)的可行性,验证了AOS在柔性电子和大面积电路中的应用潜力(图8g, h)。AOS晶体管可在较低工艺温度下制造,使其与传统硅基IC区分开来,适用于玻璃和塑料基板上的轻量、低功耗电子系统。

图8. 采用非晶氧化物半导体(AOS)的晶体管。a 总结了n型AOS半导体中的电子迁移率,高迁移率可提升显示应用中的器件速度和分辨率。b 展示显示应用中AOS晶体管内应力产生的示意图。c 基于AOS能带结构和空穴有效质量,总结p型、n型及绝缘态材料特性的关系图。d 能带图展示了使用范德华接触降低InGaZnO₄沟道接触电阻的机制。e 基于硒合金化Te-TeOₓ的p型AOS与原始状态的转移特性对比。f 用于比较不同材料体系特定性能指标的示意图。g、h 分别为采用AOS晶体管的NAND和NOR逻辑门输出特性及电路图实例。

V 先进介电材料

5.1 高K介电材料及二维材料/高K集成结构

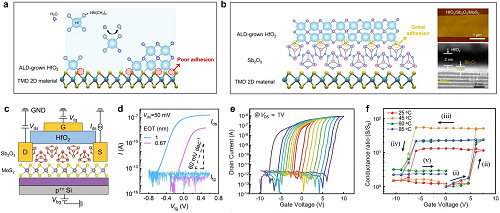

随着半导体技术的持续进步,晶体管尺寸的不断微缩、纳米级沟道长度以及栅介质的持续减薄,使传统CMOS晶体管面临短沟道效应和直接隧穿漏电流等物理限制。为应对这些挑战,主要采取两大策略:一是通过减薄沟道厚度来抑制短沟道效应,利用二维范德华材料(如MoS₂、WSe₂、BP)实现原子级厚度并保持高迁移率;二是用高K介电材料替代SiO₂以抑制隧穿漏电流,等效氧化层厚度(EOT)成为关键参数。例如,英特尔14纳米FinFET技术采用2.6纳米HfO₂介质实现了0.9纳米EOT,为低功耗应用设定了性能基准。

然而,二维材料表面无悬挂键的惰性特性给高K介质的均匀沉积带来挑战(图9a)。为实现高质量集成,需采用非破坏性沉积工艺并形成范德华界面以降低界面态密度。Xu等人提出采用三氧化二锑(Sb₂O₃)作为缓冲层,通过范德华相互作用与二维半导体形成低缺陷界面,并借助其亲水性表面通过原子层沉积均匀形成超薄高K介质堆叠(HfO₂/Al₂O₃/ZrO₂),最终在二维材料上实现了0.67纳米EOT的创纪录成果(图9b)。基于此结构的单层MoS₂ FET表现出优异的栅极控制能力,在0.4V附近出现陡峭的电流开关,亚阈值摆幅接近60 mV/dec(图9c, d),且更薄的EOT有助于降低阈值电压和工作电压。另一种策略由Li等人提出,利用PTCDA分子晶体作为成核层实现HfO₂沉积,该结构同样满足低漏电流和高击穿电场的要求,使MoS₂和WSe₂ CMOS晶体管在保持高开关比的同时,工作电压可与先进硅CMOS媲美。

综上,通过Sb₂O₃缓冲层或PTCDA分子层等界面工程技术,能够有效解决高K介质在二维材料上的集成难题,实现EOT低于1纳米、亚阈值摆幅接近热离子发射极限的低功耗晶体管,为下一代半导体器件发展提供了可行路径。

图9. 高K介质与铁电材料在现代FET中的应用。a 在二维TMD单层材料上通过原子层沉积直接生长HfO₂的质量问题示意图;b 在二维材料与高K介质层间插入1纳米厚Sb₂O₃缓冲层后ALD生长HfO₂的质量改善效果;c 采用Sb₂O₃/HfO₂双层栅介质的双栅MoS₂ FET结构示意图;d 两种不同等效氧化层厚度(EOT为1纳米和0.67纳米)的Sb₂O₃/HfO₂栅介质双栅MoS₂器件的转移特性对比;e 采用hBN/CIPS介质的α-In₂Se₃铁电FET在不同栅压扫描方向下的转移特性与滞后回线。

5.2 铁电材料

铁电介质层是铁电场效应晶体管(FeFET)的核心组件,其特性是在外电场下能保持自发极化,使FeFET可作为非易失性存储器运行,相比传统DRAM或闪存具有更低功耗和更快读写速度。此外,铁电极化的连续变化特性支持多级数据存储,提升了高密度存储应用的潜力。常见的铁电绝缘体包括锆钛酸铅(PZT)等钙钛矿材料以及氧化铪基材料(如HZO)。PZT性能优异但存在高工艺温度和含铅问题;HZO则与现有CMOS工艺兼容性更好,但其正交晶相稳定需要苛刻条件,且存在较低K值和电荷陷阱等挑战。为此,二维铁电材料(如α-In₂Se₃、SnS、CIPS)因能在原子级厚度保持极化而受到关注,它们具有高可缩放性、非易失性存储功能以及适用于神经形态计算的优势。

铁电层可与多种半导体材料集成以实现多功能FeFET。例如,基于BiFeO₃(BFO)与VO₂异质结构的铁电晶体管(图9e),其转移特性显示VO₂的金属-绝缘体转变(MIT)可通过铁电栅压进行非易失性调控,形成明显的滞回曲线,且MIT的阈值电压具有温度依赖性,表明在低功耗存储和神经形态计算中具有潜力。然而,传统FeFET受限于保持时间短、退极化场和栅极漏电流等问题。为应对这些挑战,研究者提出了铁电半导体FET(FeS-FET,其沟道本身为铁电材料)以及结合铁电绝缘体与铁电半导体的Fe₂-FET新架构。Fe₂-FET通过界面极化电荷的精确调控可实现无滞后的开关特性(图9f)。近期研究还探索了将CIPS、α-In₂Se₃等层状铁电体用于范德华异质结构,以获得更宽的存储窗口和增强的极化保持能力。这些进展共同推动了铁电介质层在神经形态计算和高性能存储器件中的耐用性、可靠性及应用前景。

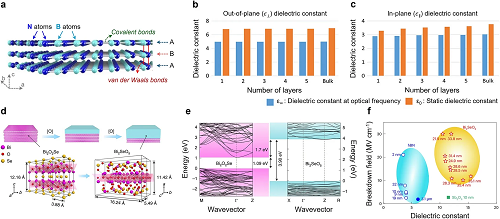

5.3 二维介电材料

介电材料在实现下一代纳米电子学中起着至关重要的作用,为高性能FET、量子器件和神经形态系统提供静电控制、电荷绝缘和界面稳定性。与传统体介电材料不同,二维介电材料具有原子级平滑表面、极少的电荷陷阱以及与范德华异质结构的强兼容性,使其对微型化和高效率电子器件极具吸引力。二维介电材料无悬挂键的结构使其能在二维/二维范德华异质结构中形成洁净界面,显著减少库仑杂质散射和界面诱导的电荷陷阱。这一洁净界面不仅提升了载流子迁移率,还通过最小化介电层/沟道界面缺陷提高了器件稳定性。

这些材料根据介电常数可分为低K和高K介电材料:低K材料有助于降低寄生电容和电荷散射,而高K材料则能增强栅极控制并抑制漏电流。六方氮化硼(hBN)是目前应用最广泛的低K二维介电材料,因其宽带隙、优异的化学和热稳定性以及强绝缘性而备受青睐。其原子结构(图10a)和介电各向异性(面外介电常数高于面内,图10b, c)使其成为最小化电荷杂质散射的理想选择。通过可控氧化得到的六方氮化硼氧化物(h-BNO)进一步增强了介电强度和耐热性。另一方面,诸如Bi₂SeO₅等高K二维氧化物(通过Bi₂O₂Se氧化获得,图10d)展现出优异的介电性能,其带隙增至3.9 eV(图10e),击穿场强与介电常数的关系(图10f)也表明其是下一代栅氧化物的有力候选者。

图10. 六方氮化硼(hBN)与二维高K介电材料的特性及应用。a hBN的晶体结构及其层数依赖的介电常数变化:b 面外介电常数(ε⊥)和c 面内介电常数(ε∥)随层数增加的变化规律。d 从Bi₂O₂Se氧化制备二维高K介质Bi₂SeO₅的工艺流程与结构演变示意图。e Bi₂O₂Se与Bi₂SeO₅的能带结构对比,展示氧化导致的带隙展宽与电子特性变化。f 二维材料介电常数与击穿电场关系的性能对比图。

VI 未来互连技术

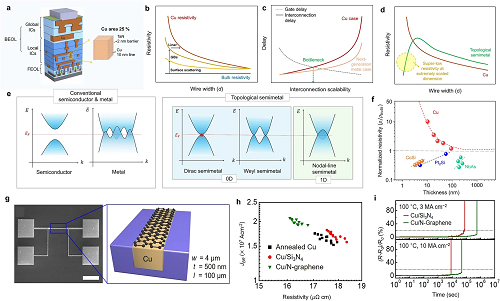

6.1 后端工艺连线的尺寸缩放

自后端工艺引入双大马士革工艺以来,铜一直是主导的互连材料。然而,铜固有的电迁移和扩散问题需要集成钽氮化物和钴等阻挡层/衬垫材料来缓解。随着晶体管尺寸缩小,互连尺寸也按比例微缩至纳米级宽度。但在双大马士革工艺中,为防止电迁移和扩散而必需的阻挡层/衬垫材料导致铜仅占互连总横截面积的25%(图11a),这种尺寸缩放加剧了RC延迟,导致高功耗。当铜互连尺寸接近纳米尺度时,由于表面散射和晶界效应增强,其电阻率会显著上升(遵循FS和MS模型),图11b显示了亚10纳米尺度下电阻率的指数级增长,从而引发严重的互连延迟问题。

为缓解铜电阻率增加问题,业界探索了钌和钴等替代衬垫/阻挡层材料,它们表现出更好的抗电迁移性和更低的晶界散射。然而,这些材料体电阻率仍高于铜,且集成工艺复杂、成本高,使得铜互连在微缩方面面临技术瓶颈(图11c)。因此,开发替代互连材料势在必行。

拓扑半金属(如TaAs、NbAs、MoP)因其受拓扑保护的表面态可实现无背散射的电子传输,展现出巨大潜力。这些材料在亚10纳米尺度下表现出极低的电阻率(图11d),能有效解决互连延迟问题。例如,TaAs纳米带结构实现了约35 μΩ cm的超低电阻率,显著优于纳米尺度的铜。此外,一维金属纳米线和二维层状金属(如TMDs中的镜像孪晶界)也因其准弹道输运、高载流能力和低电阻率,成为有前景的替代候选材料,有望克服未来亚3纳米技术节点的互连缩放挑战。

图11. 后道铜互连技术的挑战与新一代互连材料的进展。a 后道互连结构示意图,显示铜仅占25%面积,需集成氮化钽提升可靠性;b 铜线电阻率随线宽变化趋势,表明表面散射、晶界效应及制程因素是纳米尺度电阻率飙升的主因;c 互连微缩导致互连延迟与栅延迟差距扩大,需采用新一代金属材料突破瓶颈;d 拓扑半金属与传统铜的电阻率对比,拓扑材料凭借纳米尺度下无背散射电子输运展现显著优势;e 常规半导体、金属与拓扑半金属的能带结构对比,按能带交叉点维度分为0D和1D类别;f 典型拓扑半金属与传统铜在不同厚度下的电阻率趋势;g 实际互连结构的SEM图像及三维示意图展示镶嵌结构中的氮掺杂石墨烯封端铜互连;h 退火铜、氮化硅封端铜与氮掺杂石墨烯封端铜的击穿电流密度-电阻率关系,石墨烯封端表现出最优导电可靠性;i 100℃恒定电流密度下两种封端铜互连的击穿寿命对比,石墨烯封端耐久性显著提升。

6.2 超越Ti/Au接触的先进技术

随着半导体器件的持续微型化,互连材料需在可缩放性、可靠性和电性能方面取得进步。尽管铜/氮化钛电极因低电阻率和工艺兼容性而被广泛使用,但其肖特基势垒导致的高接触电阻问题在亚10纳米技术节点中仍未完全解决。为降低金属-半导体界面的接触电阻,研究者探索了多种方法,包括使用镍硅化物、钴硅化物等硅基合金,但这些方法主要适用于传统硅基器件。

对于低维半导体,金属/半导体界面的本征隧穿势垒是接触电阻的主因,因此需考虑铋或钼等替代金属。钼与半导体表面附着力强,且相比传统钛/金接触能形成更低的肖特基势垒,实验表明钼/氮化钛基接触可使接触电阻降低一个数量级,并兼容CMOS工艺。类似地,低功函数的铋作为界面材料能有效降低肖特基势垒高度,如在单层二硫化钼FET上沉积铋,可在特定载流子密度下实现123 Ω·μm的超低接触电阻。

除钼和铋基附着层外,Weyl半金属因其独特的拓扑电子特性成为颠覆性替代方案。其拓扑保护的表面态可实现近乎弹道的电荷输运,消除散射相关的电阻损耗,且无传统带隙,易于形成欧姆接触(图11e)。研究表明,基于NbAs的电极其表面导电态可贡献高达70%的总电导率,且在亚10纳米尺度下能保持低电阻率,优于铜(图11f)。尽管其电学特性优异,但将Weyl半金属集成到CMOS兼容的后端工艺仍面临高质量薄膜可控制备、图形化及沉积技术等挑战。

石墨烯封装的铜互连是另一有前景的方案,具有低电阻率、高热稳定性和抗电迁移性(图11g),在特定电流密度下表现出更长的失效时间(图11h, i)。可靠性及CMOS工艺兼容性是新材料商业化的关键要求。钼已用于半导体工艺并证明其可行性;铋在实验中表现良好但集成度较低;Weyl半金属虽具颠覆性潜力,仍需在工艺缩放和集成方面取得突破。未来研究应聚焦于可扩展沉积技术、界面优化及集成策略的开发,以克服当前后端工艺限制,满足下一代半导体器件的需求。

VII 可靠性与器件寿命

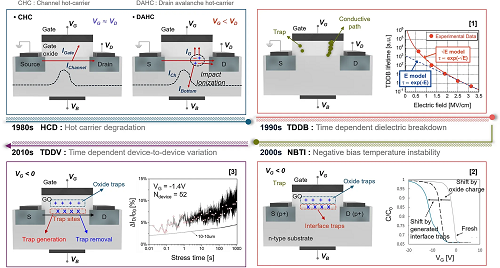

当MOSFET的尺寸微缩逼近其物理与量子力学极限时,确保器件的长期可靠性已成为维持现代电子设备性能与运行稳定性的关键。在先进半导体节点中,即便是微小的可靠性问题也可能严重损害电路功能,导致功耗增加、性能下降及器件早期失效。这对于人工智能、边缘计算和新兴量子技术等要求超低功耗、高速处理及长期耐用性的应用至关重要。多种退化机制(图12)——包括热载流子退化、时间依赖介电层击穿、负偏压温度不稳定性以及时间依赖的器件间参数波动——对器件性能、可靠性及寿命构成显著限制。随着晶体管尺寸进入亚3纳米范畴,增强的电场、显著的量子效应以及界面缺陷加速了器件退化,使这些可靠性挑战更为严峻。深入理解这些可靠性挑战并制定缓解策略,将是推动下一代半导体技术发展的基石。

图12. MOSFET器件可靠性问题概览,重点展示关键退化机制及其物理过程。沟道热载流子与漏极雪崩热载流子效应:描绘不同栅漏电压条件下碰撞电离导致的载流子注入(栅极漏电流Ig)及沟道退化;时间依赖介电层击穿:电场应力诱导栅氧层形成导电通路的过程;负偏压温度不稳定性:界面态与氧陷阱产生引起的器件特性漂移;时间依赖器件间波动:氧陷阱生成与湮灭对器件性能统计分布的影响,以及负栅偏压下实测的性能波动。

7.1 热载流子退化与漏极雪崩热载流子效应

热载流子退化(HCD)由高能载流子注入栅氧层导致,引发界面态生成和氧陷阱形成。当高栅漏电压(Vgd)在沟道内加速载流子并在漏极附近发生碰撞电离时,此现象尤为显著。当Vg ≈ Vd时,高能载流子获得足够能量越过势垒并被氧层捕获,导致沟道和栅介质逐渐退化;当Vg < Vd时,碰撞电离产生额外载流子(如nMOSFET中的空穴),加剧栅极电流并加速氧层损耗。HCD的长期影响表现为阈值电压(Vth)、亚阈值摆幅(S.S.)和迁移率(μ)等关键电学参数的漂移。为缓解HCD,需采用先进的栅堆叠工程方法,如优化沟道掺杂分布和引入应变工程技术。

7.2 时间依赖介电层击穿

时间依赖介电层击穿(TDDB)是MOSFET中因栅氧层长期承受高电场而逐步退化引发的可靠性问题。当应力诱导缺陷在介质中积累至形成导电渗流路径时,将发生灾难性击穿。击穿速率与电场强度呈指数关系(遵循E模型或√E模型)。高K介质材料(如HfO₂、ZrO₂、Al₂O₃)虽能通过增加物理厚度维持高栅电容、减少直接隧穿漏电,但TDDB在激进微缩器件中仍是严峻挑战。缓解策略包括:通过氮化(如HfSiON)抑制氧空位;在high-K介质与硅衬底间插入超薄SiO₂界面层以降低缺陷密度;采用O₂或N₂等离子体处理钝化界面悬挂键。

7.3 负偏压温度不稳定性

负偏压温度不稳定性(NBTI)主要影响pMOSFET,表现为长时间负栅偏压下Si/SiO₂界面态生成和空穴被氧陷阱捕获,导致Vth漂移。其严重程度与应力时间和温度呈幂律关系,且在应力移除后存在部分恢复效应。通过采用氮钝化high-K介质、优化Si/SiO₂界面氢终止等栅堆叠工程可有效抑制NBTI。

7.4 时间依赖的器件间参数波动

当MOSFET尺寸持续缩小时,制造过程中的随机波动会引入显著的器件性能差异。时间依赖的器件间参数波动(TDDV)源于氧陷阱生成和移除的随机性,导致器件群体的电学特性发生不可预测的漂移。研究表明,采用碱金属氟化物(如LiF)作为介质覆盖层可改善性能并抑制环境影响。氧陷阱动态还会引起类似随机电报噪声的波动,增加Vth差异和驱动电流不均匀性(图12)。解决TDDV需提升工艺均匀性、优化缺陷管理策略并开发能够预测氧陷阱随机变化的模型。

7.5 可靠性增强的未来展望及新兴材料挑战

未来需通过多层面策略增强可靠性:材料与工艺层面,开发高稳健性的新型high-K介质、优化沟道掺杂和应变工程;模型层面,整合基于物理的退化模型和机器学习辅助预测技术;电路设计层面,采用自适应偏置、误差校正和动态补偿电路来抵消随机波动。

在新兴材料中,可靠性挑战呈现新特点:对于二维材料,因其原子级厚度和高比表面积,对环境相互作用、介质界面电荷陷阱和接触不稳定性高度敏感,导致Vth漂移和滞后现象。需通过精细界面工程和介质选择来优化。对于钙钛矿材料,场致和光致离子迁移会引发动态陷阱形成、相分离和滞后,类似TDDB和NBTI的不稳定性。可通过离子陷阱钝化、组分工程和界面阻挡层来缓解。对于莫特材料,其强关联电子系统会表现出独特的降解行为,如场致介电击穿(莫特隙突然崩塌导致绝缘体-金属转变)和电阻开关器件中的细丝形成。需通过界面工程、器件设计调谐和脉冲优化来稳定其开关行为。

总之,应对MOSFET的可靠性挑战需要采取综合策略。随着技术向亚3纳米及更小节点推进,确保器件可靠性将始终是一项基础性挑战,要求半导体可靠性工程领域持续创新。

VIII 前景与展望

8.1 应对器件局限性的关键视角

半导体器件的持续微缩带来了偏压热不稳定性、漏电流以及开关性能等方面的严峻挑战。为克服这些局限,必须探索新材料、新器件架构和优化策略。本节讨论了缓解BTI、解决漏电问题及实现高性能开关特性的关键方法,重点介绍了氧化物半导体晶体管、混合介电工程和浮栅晶体管架构的最新进展。图13概述了应对这些挑战的各种策略。

图13. BTI缓解、漏电流抑制与高性能开关技术的优化策略。a-d 不同偏压应力下非晶IGZO晶体管的转移特性曲线,展示氮掺杂对阈值电压漂移(ΔVth)的抑制效果;e-g 超薄铪锆氧化物(HZH)混合铁电栅堆叠在漏电流抑制方面的性能优势:e 集成2纳米HZH栅堆叠(萤石结构多层膜)的晶体管结构示意图;f HZH多层栅堆叠的漏电流与等效氧化层厚度关系(蓝色),对比文献报道的高K金属栅数据(红色为层间清除的2纳米HfO₂,灰色为掺杂HfO₂,黑色为SiO₂/多晶硅),HZH在6.5Å EOT下实现最低漏电流;g 集成2纳米HZH的长沟道晶体管载流子迁移率与EOT关系(蓝色),对比工业级2纳米HfO₂器件(红色),HZH无需界面清除即可实现超薄EOT且迁移率更高。h-j 浮栅晶体管系统实现的高性能开关特性:h 以MoS₂为沟道、hBN为隧穿层、控制栅精确调控电荷的浮栅结构示意图;i 不同控制栅偏压下的转移特性;j 编程/擦除循环后的长期稳定性测试,表明其在先进电子器件中具备可靠高性能运行潜力。

8.1.1 缓解偏压热不稳定性

BTI是TFT中一个重要的可靠性挑战, prolonged的偏压应力会导致阈值电压漂移,影响器件长期性能。这种退化在非晶氧化物半导体(如a-IGZO)中常见,缺陷位点的电荷 trapping 是Vth不稳定的主因。图13a-d显示了未掺杂和氮掺杂a-IGZO晶体管在室温和高温下不同偏压应力条件下的转移特性。数据显示,氮掺杂样品通过调节缺陷态和减轻界面电荷 trapping,显著提高了Vth稳定性,尤其是在高温下有效抑制了Vth漂移和“驼峰”效应。为提高BTI耐受性,还需采用钝化技术和界面工程策略。高迁移率氧化物半导体结合优化掺杂策略,为稳定高性能TFT技术提供了可行路径。

8.1.2 解决漏电问题

激进微缩晶体管的一个持续挑战是栅介质的漏电流。传统高K材料(如Al2O3)虽能提高电容,但常因界面粗糙度和缺陷处电荷散射导致高漏电。采用混合介质堆叠是有效的解决方案。例如,将聚合物绝缘体PMMA与Al2O3结合形成的混合介质系统,能更可控地调节界面电场,抑制缺陷辅助导电,从而提高晶体管稳定性和场效应迁移率,并有效降低Ig。

最近的研究引入了HfO₂–ZrO₂超晶格异质结构作为栅介质(图13e)。与传统HfO2堆叠不同,HZH无需SiO₂清除工艺即可实现超薄介质微缩(EOT低至6.5 Å),有助于保持洁净界面,从而显著抑制漏电流(图13f),并保持高载流子迁移率(图13g)。这些进展凸显了多介质堆叠在维持高性能的同时降低漏电的潜力,为下一代器件提供了可扩展、高能效的解决方案。

8.1.3 实现超越硅基MOSFET的高性能开关

为超越硅基MOSFET的固有限制,未来研究需聚焦于将新兴半导体(如二维材料、钙钛矿、氧化物半导体等)与成熟且不断演进的高K介质、铁电介质等材料进行战略集成。浮栅晶体管架构是这一方向的典范。图13h-j展示了一种采用MoS2沟道、多层hBN隧道势垒和控制栅的浮栅晶体管系统。该结构通过hBN隧穿层和阻挡层实现有效的电荷存储与调制(图13h),转移特性显示出稳健的开关行为和明显的滞回效应(图13i),长期稳定性测量也证实了即使在多次编程/擦除循环后仍具有优异的电荷保持能力(图13j),使其非常适用于非易失性存储器和逻辑应用。

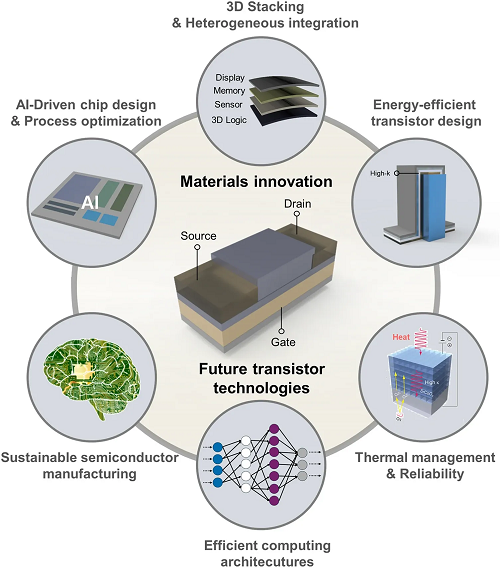

8.2 晶体管制造展望

图14. 面向材料创新的未来晶体管技术前景与展望。重点应对半导体行业的关键挑战:偏压热不稳定性抑制、漏电问题解决及高性能开关特性实现;推进热管理方案与三维堆叠架构以提升器件性能与集成密度;探索新兴计算范式及与人工智能的融合技术以满足持续演进的技术需求;通过可持续制造与高能效处理确保行业长期发展潜力。

晶体管的持续微型化已将半导体技术推向基础缩放极限,需要寻求超越传统平面CMOS缩放的新方案。随着功耗、互连电阻和热约束成为主导性挑战,三维堆叠、高能效晶体管架构和AI驱动计算范式正成为下一代半导体器件的基础。

三维堆叠架构通过集成异质计算单元、减少互连延迟和提高系统级效率,使行业能够超越晶体管密度缩放。先进封装技术(如Foveros、3D Fabric)利用芯粒堆叠和混合键合实现高带宽、低延迟。面向未来,单片三维集成可将晶体管层垂直堆叠在同一晶圆上,实现超高互连密度和能效。然而,该技术面临互连电阻(需探索纳米线、二维金属等新材料)、热耗散(需采用高导热材料如石墨烯、碳纳米管和微流体冷却等主动技术)以及与CMOS工艺兼容性等挑战。与二维材料FET、铁电FET等新兴晶体管的异质集成将进一步扩展其功能。

提升能效方面,研究聚焦于超低阈值电压器件和突破60 mV/dec亚阈值摆幅热力学极限。隧道FET、负电容FET和狄拉克源FET等新架构,结合二维材料的无缺陷范德华界面,有望实现陡峭斜率开关,显著降低AI加速器、物联网等应用的功耗。但需平衡低电压操作与泄漏控制,并解决与现有CMOS工艺的集成问题。

热管理对于三维堆叠芯片和高功率计算至关重要。被动解决方案采用高导热材料(如金刚石界面材料)进行热扩散;主动技术如微流体冷却和热电冷却可动态调节散热。结合AI驱动的动态热管理和热感知任务调度,能实现预测性热调控,保障高性能计算的稳定运行。

新功能集成方面,神经形态计算利用忆阻器、铁电 synapse等新兴材料模拟突触可塑性,实现存算一体和事件驱动处理,大幅提升AI能效。神经形态感知设备(如仿视网膜视觉传感器、仿皮肤触觉传感器)可实现高效的数据感知与处理。这些硬件与AI算法的协同设计是发挥其潜力的关键。

可持续制造涉及开发低功耗晶体管(如TFET)、采用氮化镓等环保材料、利用EUV光刻减少化学品消耗,以及通过AI优化和可再生能源降低碳足迹。

与AI的整合体现在多个层面:内存计算架构(如FeFET、RRAM)通过减少数据移动加速AI推理;AI优化的晶体管(如NC-FET、二维半导体FET)实现动态阈值调节和超低功耗处理;AI本身也用于半导体设计优化和工艺控制,加速新器件开发。未来,AI原生半导体平台将通过材料、器件和系统架构的协同设计,最大化AI性能。

作者简介

关于我们

Nano-Micro Letters《纳微快报(英文)》是上海交通大学主办、在Springer Nature开放获取(open-access)出版的学术期刊,主要报道纳米/微米尺度相关的高水平文章(research article, review, communication, perspective, highlight, etc),包括微纳米材料与结构的合成表征与性能及其在能源、催化、环境、传感、电磁波吸收与屏蔽、生物医学等领域的应用研究。已被SCI、EI、PubMed、SCOPUS等数据库收录,2024 JCR IF=36.3,学科排名Q1区前2%,中国科学院期刊分区1区TOP期刊。多次荣获“中国最具国际影响力学术期刊”、“中国高校杰出科技期刊”、“上海市精品科技期刊”等荣誉,2021年荣获“中国出版政府奖期刊奖提名奖”。欢迎关注和投稿。

Web: https://springer.com/40820

E-mail: editor@nmlett.org

Tel: 021-34207624

如果文章对您有帮助,可以与别人分享!:Nano-Micro Letters » 首尔国立大学Ho Won Jang等综述:跨越硅基极限,新型晶体管材料演变

Nano-Micro Letters

Nano-Micro Letters 西工大叶谦、刘旭庆团队:碳点插层MXene界面调控赋能柔性水凝胶高效电磁吸收

西工大叶谦、刘旭庆团队:碳点插层MXene界面调控赋能柔性水凝胶高效电磁吸收 朱美芳院士/潘绍武研究员等: MXene组装的液态金属杂化微颗粒赋能多功能可拉伸印刷电子

朱美芳院士/潘绍武研究员等: MXene组装的液态金属杂化微颗粒赋能多功能可拉伸印刷电子 热烈祝贺!Nano-Micro Letters 优秀青年编委入选名单揭晓

热烈祝贺!Nano-Micro Letters 优秀青年编委入选名单揭晓 江苏科大于超&上海交大巩伟等综述:多孔功能纳米材料用于连续流催化

江苏科大于超&上海交大巩伟等综述:多孔功能纳米材料用于连续流催化